SJ 50597/33-1995

基本信息

标准号: SJ 50597/33-1995

中文名称:半导体集成电路 JB200型CMOS双路单刀单掷模拟开关详细规范

标准类别:电子行业标准(SJ)

英文名称:Semiconductor integrated circuits-Detail specification for Type JB200 CMOS dual SPST analog switch

标准状态:现行

发布日期:1995-05-25

实施日期:1995-12-01

下载格式:pdf zip

标准分类号

中标分类号:仪器、仪表>>仪器、仪表综合>>N01技术管理

关联标准

出版信息

页数:27页

标准价格:20.0

相关单位信息

标准简介

标准图片预览

标准内容

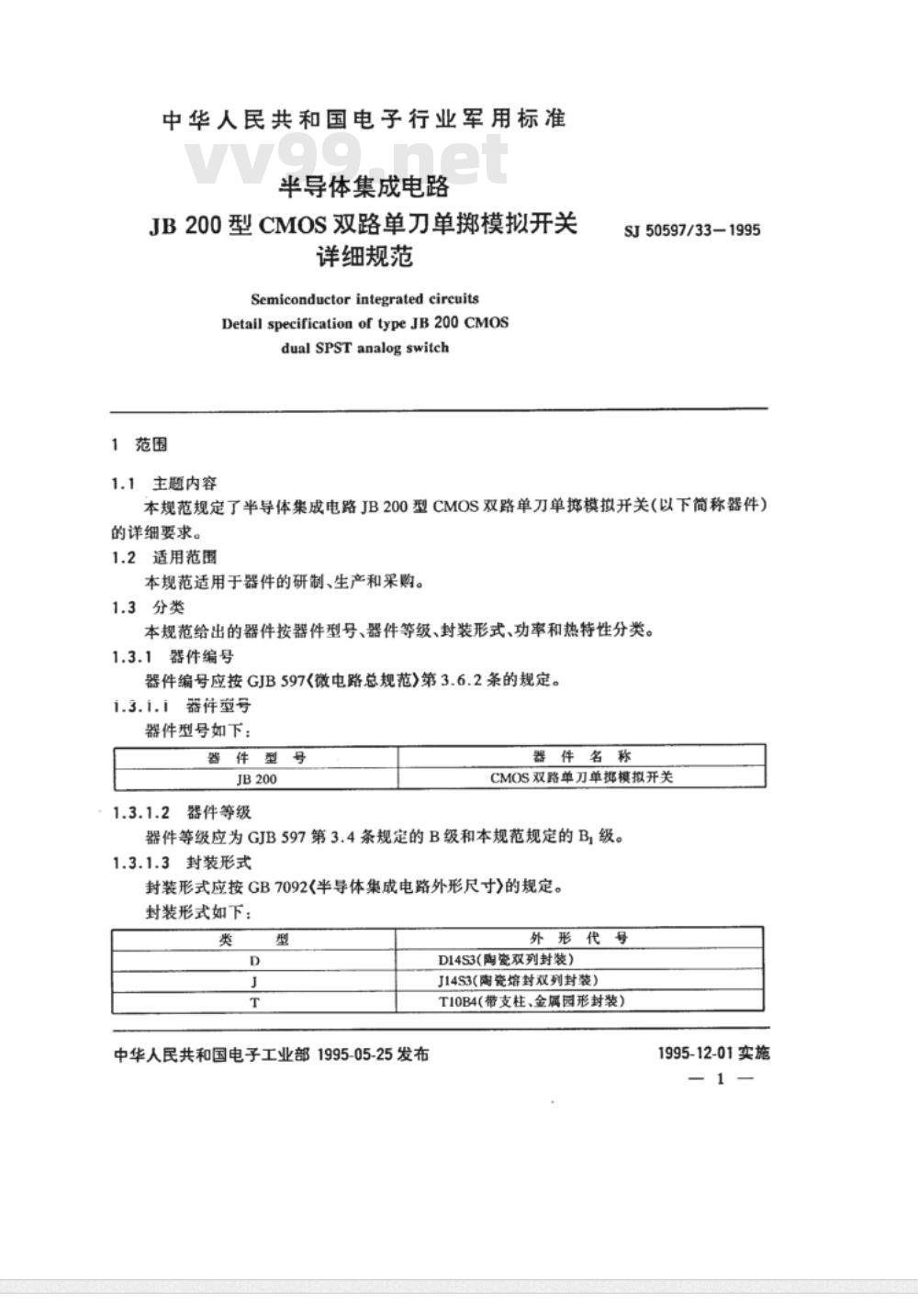

中华人民共和国电子行业军用标准FL5962

SJ50597/33-1995

半导体集成电路

JB200型CMOS双路单刀单掷模拟

开关详细规范

Semiconductor integrated circuitsDetail specification of type JB 200 CMOSdualSPSTanalogswitch

1995-05-25发布

1995-12-01实施

中华人民共和国电子工业部

中华人民共和国电子行业军用标准半导体集成电路

JB200型CMOS双路单刀单掷模拟开关详细规范

Semiconductor integrated circuitsDetail specification of type JB200 CMOSdual SPST analog switch

主题内容

SJ50597/331995

本规范规定了半导体集成电路JB200型CMOS双路单刀单掷模拟开关(以下简称器件)的详细要求。

1.2适用范围

本规范适用于器件的研制、生产和采购。1.3分类

本规范给出的器件按器件型号、器件等级、封装形式、功率和热特性分类。1.3.1器件编号

器件编号应按GJB597<微电路总规范》第3.6.2条的规定。1.3.1.1器件型号

器件型号如下:

器件型号

1.3.1.2器件等级免费标准下载网-唯久标准网vv99

器件名称

CMOS双路单刀单挪模拟开关

器件等级应为GJB597第3.4条规定的B级和本规范规定的B级。1.3.1.3封装形式

封装形式应按GB7092(半导体集成电路外形尺寸>的规定。封装形式如下:

中华人民共和国电子工业部1995-05-25发布外形代号

D14S3(陶瓷双列封装)

J14S3(陶瓷焙封双列封装)

T10B4(带支柱、金属园形封装)1995-12-01实施

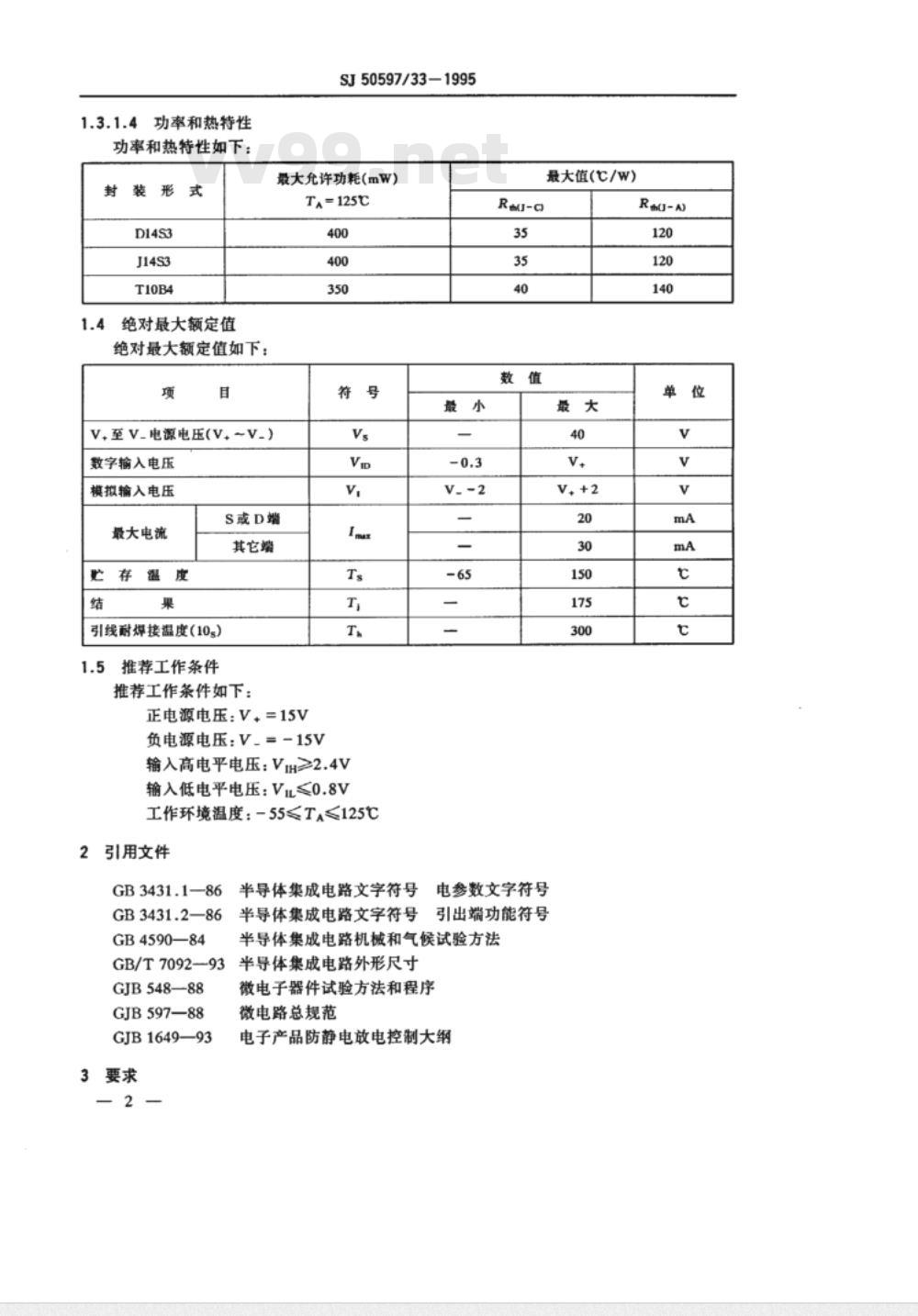

1.3.1.4功率和热特性

功率和热特性如下:

装形式

绝对最大额定值

绝对最大额定值如下:

V,至V.电源电压(V.~V.)

数字输入电压

模拟输入电压

最大电流

引线耐焊接温度(10s)

推荐工作条件

SJ50597/33-1995

最大允许功耗(mW)

TA=125C

S或D端

其它端

推荐工作条件如下:

正电源电压:V.=15V

负电源电压:V_=-15V

输入高电平电压:V≥2.4V

输入低电平电压:Vu≤0.8V

工作环境温度:-55≤T≤125℃

引用文件

GB 3431.1—86

GB3431.2—86

GB4590—84

GB/T7092—93

GJB548—88

GJB597—88

GJB1649—93

3要求

半导体集成电路文字符号

半导体集成电路文字符号

最大值(t/w)

电参数文字符号

引出端功能符号

半导体集成电路机械和气候试验方法半导体集成电路外形尺寸

微电子器件试验方法和程序

微电路总规范

电子产品防静电放电控制大纲

详细要求

SJ50597/33-1995

各项要求应按GJB597和本规范的规定。本规范规定和B级器件仅在产品保证规定的筛选、鉴定和质量一致性检验的某些项目和要求不同于B级。

设计结构和外形尺寸

设计结构和外形尺寸应符合GJB597和本规范的规定3.2.1引出端排列

引出端排列应符合图1的规定。引出端排列为俯视图。D14S3、J14S3引出端排列:

T10B4引出端排列:

功能表

引出端排列

功能表如下:

3.2.3功能框图

输入电压

2.4V6V,≤15V

0≤V≤0.8V

功能框图应符合图2的规定。

3.2.4电路图

SJ 50597/331995

及驱动

2功能框图(号)

开关状态

制造厂在鉴定前应将电路图提交给鉴定机构,各制造厂的电路图应由鉴定机构存档备查。3.2.5封装形式

封装形式应按本规范1.3.1.3条的规定。3.3引线材料和涂覆

引线材料和涂覆应按GJB597第3.5.6条的规定。3.4电特性

电特性应符合表1的规定。

键合应按GJB597第3.7.1.1条的规定。特

输入端关断漏电流

输出端关断漏电流

开关导通漏电流

输入低电平电流

输入高电平电流

正电源电流

负电源电流

控制端输入电容

开关输入电容

开关输出电容

开关导通时间

开关关断时间

关断隔离度2)

通道串扰3)

Iyotom

SJ50597/33-1995

表1电特性

(若无其他规定,V.=15V.V.=-15V)V=0.8V

V(s)=10v

D)=-1mA

Vrs)=-10V

[u(D)=ImA

Vus)=14V

VD)=~14V

Vus)=-14V

VD)=14V

VDy\14V

Vus)=-14V

VkD)-14V

Vns)=14V

VKD)=Vs=14V

VrD) = Vs

Vi=15V

V=0V或

Vn=0V或

T=25,-55

TA=12SC

T=25,-55

TA=125C

TA=25t

T=125,-55

Ta=25t

TA=125,-55

Ta=25t

T^=125,-55

Ta=25t

Ta=125C,-55

Ta=25C

T=125C,~55

TA=25t

T=125-55

Ta=25C

TA=125C,55C

TA=25C

TA-125C.5ST

TA-25℃125

TA--55C

T=25,125

TA--55C

T=25,GND=0V,V=0V,=1MHz

T^=25C,CND=0V,VH=5V,f=1MH

Ta=25C.CND=0V,Vm=5V,f=1MH

C=100pF

RL=1KO

C,=100pF

Rt=1kn

T=25℃.-55℃

TA=125C

TA=25C,

TA=125C

Ta=25,V=1V,f=200kHz

Ta-25cV-1V,f=200kHz

注:1)仅在初始鉴定及当工艺和设计发生变化有可能影响输入电容时进行测试。大

SJ50597/33-1995

2)仅在初始鉴定及当工艺和设计发生变化时进行测试。电试验要求

器件的电试验要求应为表2所规定的有关分组,各分组的电测试按表3的规定。电试验要求

中间(老化前)电测试

中间(老化后)电测试

最终电测试

A组试验要求

C组终点电测试

C组检验增加的电试验分组

D组终点电测试

A2、A3、A42)、A9

Al.A2.A3.A42\.A9.A10.A1l

A1和表4的△极限

不要求

(见表3)

B,级器件

A2、A3、A42\、A9

A1.A2.A3.A42\A9

A1和表4的△极限

注:1)该分组要求PDA计算(见本规范4.2条)。2)该分组仅在初始鉴定和当工艺或设计改变时进行。对Cr、Cis和Cos进行测量时,在被测量的输入端和地之间连接电容电桥,f=1MHz。6

SJ 50597/33—1995

被测螨

剩试号

SJ 50597/331995

被测鞘

测试母

SJ 50597/33-1995

被测端

剩试号

eaerpy

SJ50597/33-1995

被测端

测试母

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。

SJ50597/33-1995

半导体集成电路

JB200型CMOS双路单刀单掷模拟

开关详细规范

Semiconductor integrated circuitsDetail specification of type JB 200 CMOSdualSPSTanalogswitch

1995-05-25发布

1995-12-01实施

中华人民共和国电子工业部

中华人民共和国电子行业军用标准半导体集成电路

JB200型CMOS双路单刀单掷模拟开关详细规范

Semiconductor integrated circuitsDetail specification of type JB200 CMOSdual SPST analog switch

主题内容

SJ50597/331995

本规范规定了半导体集成电路JB200型CMOS双路单刀单掷模拟开关(以下简称器件)的详细要求。

1.2适用范围

本规范适用于器件的研制、生产和采购。1.3分类

本规范给出的器件按器件型号、器件等级、封装形式、功率和热特性分类。1.3.1器件编号

器件编号应按GJB597<微电路总规范》第3.6.2条的规定。1.3.1.1器件型号

器件型号如下:

器件型号

1.3.1.2器件等级免费标准下载网-唯久标准网vv99

器件名称

CMOS双路单刀单挪模拟开关

器件等级应为GJB597第3.4条规定的B级和本规范规定的B级。1.3.1.3封装形式

封装形式应按GB7092(半导体集成电路外形尺寸>的规定。封装形式如下:

中华人民共和国电子工业部1995-05-25发布外形代号

D14S3(陶瓷双列封装)

J14S3(陶瓷焙封双列封装)

T10B4(带支柱、金属园形封装)1995-12-01实施

1.3.1.4功率和热特性

功率和热特性如下:

装形式

绝对最大额定值

绝对最大额定值如下:

V,至V.电源电压(V.~V.)

数字输入电压

模拟输入电压

最大电流

引线耐焊接温度(10s)

推荐工作条件

SJ50597/33-1995

最大允许功耗(mW)

TA=125C

S或D端

其它端

推荐工作条件如下:

正电源电压:V.=15V

负电源电压:V_=-15V

输入高电平电压:V≥2.4V

输入低电平电压:Vu≤0.8V

工作环境温度:-55≤T≤125℃

引用文件

GB 3431.1—86

GB3431.2—86

GB4590—84

GB/T7092—93

GJB548—88

GJB597—88

GJB1649—93

3要求

半导体集成电路文字符号

半导体集成电路文字符号

最大值(t/w)

电参数文字符号

引出端功能符号

半导体集成电路机械和气候试验方法半导体集成电路外形尺寸

微电子器件试验方法和程序

微电路总规范

电子产品防静电放电控制大纲

详细要求

SJ50597/33-1995

各项要求应按GJB597和本规范的规定。本规范规定和B级器件仅在产品保证规定的筛选、鉴定和质量一致性检验的某些项目和要求不同于B级。

设计结构和外形尺寸

设计结构和外形尺寸应符合GJB597和本规范的规定3.2.1引出端排列

引出端排列应符合图1的规定。引出端排列为俯视图。D14S3、J14S3引出端排列:

T10B4引出端排列:

功能表

引出端排列

功能表如下:

3.2.3功能框图

输入电压

2.4V6V,≤15V

0≤V≤0.8V

功能框图应符合图2的规定。

3.2.4电路图

SJ 50597/331995

及驱动

2功能框图(号)

开关状态

制造厂在鉴定前应将电路图提交给鉴定机构,各制造厂的电路图应由鉴定机构存档备查。3.2.5封装形式

封装形式应按本规范1.3.1.3条的规定。3.3引线材料和涂覆

引线材料和涂覆应按GJB597第3.5.6条的规定。3.4电特性

电特性应符合表1的规定。

键合应按GJB597第3.7.1.1条的规定。特

输入端关断漏电流

输出端关断漏电流

开关导通漏电流

输入低电平电流

输入高电平电流

正电源电流

负电源电流

控制端输入电容

开关输入电容

开关输出电容

开关导通时间

开关关断时间

关断隔离度2)

通道串扰3)

Iyotom

SJ50597/33-1995

表1电特性

(若无其他规定,V.=15V.V.=-15V)V=0.8V

V(s)=10v

D)=-1mA

Vrs)=-10V

[u(D)=ImA

Vus)=14V

VD)=~14V

Vus)=-14V

VD)=14V

VDy\14V

Vus)=-14V

VkD)-14V

Vns)=14V

VKD)=Vs=14V

VrD) = Vs

Vi=15V

V=0V或

Vn=0V或

T=25,-55

TA=12SC

T=25,-55

TA=125C

TA=25t

T=125,-55

Ta=25t

TA=125,-55

Ta=25t

T^=125,-55

Ta=25t

Ta=125C,-55

Ta=25C

T=125C,~55

TA=25t

T=125-55

Ta=25C

TA=125C,55C

TA=25C

TA-125C.5ST

TA-25℃125

TA--55C

T=25,125

TA--55C

T=25,GND=0V,V=0V,=1MHz

T^=25C,CND=0V,VH=5V,f=1MH

Ta=25C.CND=0V,Vm=5V,f=1MH

C=100pF

RL=1KO

C,=100pF

Rt=1kn

T=25℃.-55℃

TA=125C

TA=25C,

TA=125C

Ta=25,V=1V,f=200kHz

Ta-25cV-1V,f=200kHz

注:1)仅在初始鉴定及当工艺和设计发生变化有可能影响输入电容时进行测试。大

SJ50597/33-1995

2)仅在初始鉴定及当工艺和设计发生变化时进行测试。电试验要求

器件的电试验要求应为表2所规定的有关分组,各分组的电测试按表3的规定。电试验要求

中间(老化前)电测试

中间(老化后)电测试

最终电测试

A组试验要求

C组终点电测试

C组检验增加的电试验分组

D组终点电测试

A2、A3、A42)、A9

Al.A2.A3.A42\.A9.A10.A1l

A1和表4的△极限

不要求

(见表3)

B,级器件

A2、A3、A42\、A9

A1.A2.A3.A42\A9

A1和表4的△极限

注:1)该分组要求PDA计算(见本规范4.2条)。2)该分组仅在初始鉴定和当工艺或设计改变时进行。对Cr、Cis和Cos进行测量时,在被测量的输入端和地之间连接电容电桥,f=1MHz。6

SJ 50597/33—1995

被测螨

剩试号

SJ 50597/331995

被测鞘

测试母

SJ 50597/33-1995

被测端

剩试号

eaerpy

SJ50597/33-1995

被测端

测试母

小提示:此标准内容仅展示完整标准里的部分截取内容,若需要完整标准请到上方自行免费下载完整标准文档。